5-1

# CSE 30321 Computer Architecture I

#### Lecture 16 - Multi Cycle Machines

*Michael Niemier* Department of Computer Science and Engineering

|                                         | Action for R-type                           | Action for memory-reference | Action for     | Action for      |  |  |  |

|-----------------------------------------|---------------------------------------------|-----------------------------|----------------|-----------------|--|--|--|

| Step name                               | instructions                                | instructions                | branches       | jumps           |  |  |  |

| Instruction fetch                       | IR = Mem[PC],                               |                             |                |                 |  |  |  |

|                                         |                                             | PC = PC + 4                 |                |                 |  |  |  |

| Instruction                             |                                             | A =RF [IR[25:21]],          |                |                 |  |  |  |

| decode/register fetch                   |                                             | B = RF [IR[20:16]],         |                |                 |  |  |  |

|                                         | ALUOut = PC + (sign-extend (IR[1:-0]) << 2) |                             |                |                 |  |  |  |

| Execution, address                      | ALUOut = A op B                             | ALUOut = A + sign-extend    | if (A =B) then | PC = PC [31:28] |  |  |  |

| computation, branch/<br>jump completion |                                             | (IR[15:0])                  | PC = ALUOut    | (IR[25:0]<<2)   |  |  |  |

| Memory access or R-type                 | RF [IR[15:11]] =                            | Load: MDR = Mem[ALUOut]     |                |                 |  |  |  |

| completion                              | ALUOut                                      | or                          |                |                 |  |  |  |

|                                         |                                             | Store: Mem[ALUOut]= B       |                |                 |  |  |  |

| Memory read completion                  |                                             | Load: RF[IR[20:16]] = MDR   |                |                 |  |  |  |

5-2

IINI

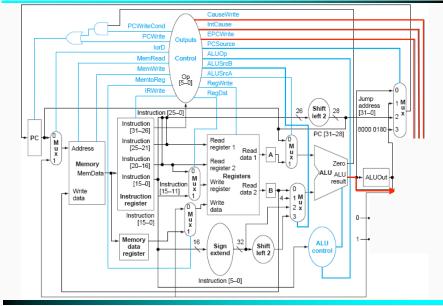

#### 斡 **Control Signals PC: PCWrite**, PCSourc **PCWriteCond**, ALUOp **PCSource** ALUSICB □ Memory: lorD, ALUSrcA MemRead, **MemWrite** Jump address [31–0] Shift 28 Instruction Instructi Instruction [31-26] **Register:** PC [31-28] Instruction [25-21] Read **IRWrite** + Address egister Instruction [20-16] data ' heaf **Register File:** Zero Memory MemData ALU ALU ++ ALUOUt Instruction [15–0] **RegWrite**, result Write data MemtoReg, register RegDst Instruction [15-0] □ ALU: Memory data register ALUSrcA, ALUSrcB, ALUOp, Instruction [5-0]

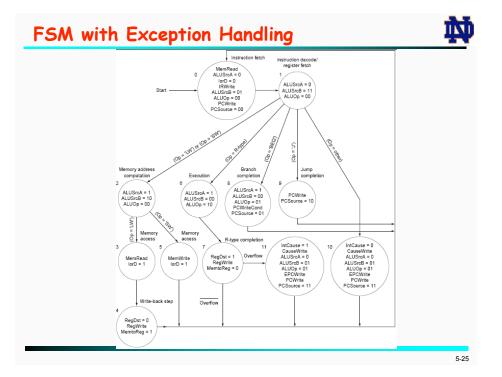

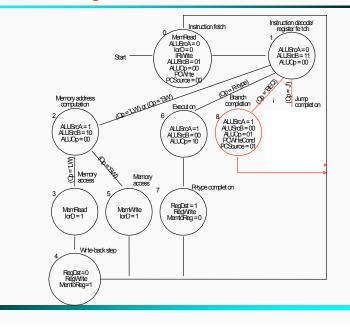

#### Finite State Diagram

#### Microprogramming as an Alternative

5-7

Control unit can easily reach thousands of states with hundreds of different sequences.

- A large set of instructions and/or instruction classes (x86)

- Different implementations with different cycles per instruction

- $\hfill\square$  Flexibility may be needed in the early design phase

- □ How about borrowing the ideas from what we just learned?

- Treat the set of control signals to be asserted in a state as an *instruction* to be executed (referred to as microinstructions)

- Treat state transitions as an instruction sequence

- Define formats (mnemonics)

- Specify control signals symbolically using microinstructions

# Microprogramming as an Alternative (cont'd) 🚺

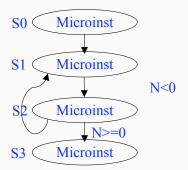

Each state => one microinstruction

IN

5-5

IN

- State transitions => microinstruction sequencing

- Setting up control signals => executing microinstructions

- To specify control, we just need to write microprograms (or microcode)

# Microinstruction Format (2)

| Field name          | Value        | Signals active                         | Comment                                                                                                          |

|---------------------|--------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------|

|                     | Add          | ALUOp = 00                             | Cause the ALU to add.                                                                                            |

| ALU control         | Sub          | ALUOp = 01                             | Cause the ALU to subtract; this implements the compare for branches.                                             |

|                     | Func code    | ALUOp = 10                             | Use the instruction's func to determine ALU control.                                                             |

| SRC1                | PC           | ALUSrcA = 0                            | Use the PC as the first ALU input.                                                                               |

|                     | Α            | ALUSrcA = 1                            | Register A is the first ALU input.                                                                               |

|                     | В            | ALUSrcB= 00                            | Register B is the second ALU input.                                                                              |

|                     | 4            | ALUSrc = 01                            | Use 4 as the second ALU input.                                                                                   |

|                     | Extend       | ALUSrcB= 10                            | Use output of the sign ext unit as the 2nd ALU input.                                                            |

|                     | Extshft      | ALUSrcB= 11                            | Use output of shift-by-two unit as the 2nd ALU input.                                                            |

|                     | Read         |                                        | Read two registers using the rs and rt fields of the IR and putting the data into registers A and B.             |

| Register<br>control | Write<br>ALU | RegWrite,<br>RegDst = 1,<br>MemtoReg=0 | Write a register using the rd field of the IR as the register number and the contents of the ALUOut as the data. |

|                     | Write<br>MDR | RegWrite,<br>RegDst = 0,<br>MemtoReg=1 | Write a register using the rt field of the IR as the register number and the contents of the MDR as the data.    |

# **Microinstruction Format (1)**

# Group the control signals according to how they are used

### □ For the 5-cycle MIPS organization:

- Memory: IorD, MemRead, MemWrite

- Instruction Register: IRWrite

- **PC:** PCWrite, PCWriteCond, PCSource

- Register File: RegWrite, MemtoReg, RegDst

(for ALU)

ALU: ALUSrcA, ALUSrcB, ALUOp

#### Group them as follows:

- Memory (for both Memory and Instruction Register)

- PC write control (for PC)

- Register control (for Register File)

- ALU control

- SRC1

- SRC2

- Sequencing

5-6

#### **Microinstruction Format (3)**

| - |     | 2        |

|---|-----|----------|

| Т | L L | 1        |

|   | - 1 | 9        |

|   |     | <b>1</b> |

| Field name          | Value           | Signals active             | Comment                                                                                           |

|---------------------|-----------------|----------------------------|---------------------------------------------------------------------------------------------------|

|                     | Read PC         | MemRead,<br>lorD = 0       | Read memory using the PC as address; write result into IR (and the MDR).                          |

| Memory              | Read ALU        | MemRead,<br>lorD = 1       | Read memory using the ALUOut as address; write result into MDR.                                   |

|                     | Write ALU       | MemWrite,<br>lorD = 1      | Write memory using the ALUOut as address, contents of B as the data.                              |

| PC write<br>control | ALU             | PCSource 00<br>PCWrite     | Write the output of the ALU into the PC.                                                          |

|                     | ALUOut-<br>cond | PCSource=01<br>PCWriteCond | , If the Zero output of the ALU is active, write the PC with the contents of the register ALUOut. |

|                     | jump<br>address | PCSource=10<br>PCWrite     | , Write the PC with the jump address from the instruction.                                        |

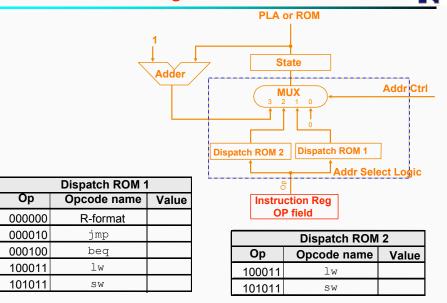

|                     | Seq             | AddrCtl = 11               | Choose the next microinstruction sequentially.                                                    |

| Sequencing          | Fetch           | AddrCtl = 00               | Go to the first microinstruction to a new instruction.                                            |

|                     | Dispatch 1      | AddrCtl = 01               | Dispatch using the ROM 1.                                                                         |

|                     | Dispatch 2      | AddrCtl = 10               | Dispatch using the ROM 2.                                                                         |

# Sample Microinstruction (1)

#### □ IFetch: IR = Mem[PC], PC = PC+4

| PCWrite:<br>PCWriteCond<br>IorD:<br>MemRead:<br>IRWrite: | 1<br>:<br>0<br>1 |               |    |   | RegCtrl | Memory | PCWrite |      |

|----------------------------------------------------------|------------------|---------------|----|---|---------|--------|---------|------|

|                                                          | 00               | Sequen<br>Add | PC | 4 |         | ReadPC | ALU     | Seq  |

| ALUSrcB:<br>ALUSrcA:<br>RegWrite:<br>RegDst:             | 01<br>0          |               |    |   |         |        |         |      |

| AddrCtrl:                                                | 11               |               |    |   |         |        |         | 5-10 |

### Sample Microinstruction (2)

# 种

**PCWrite:**

ALUOp:

ALUSrcB:

ALUSrcA: RegWrite: RegDst: AddrCtrl:

IorD: MemRead: IRWrite: MemtoReg: PCSource:

PCWriteCond: 1

01

01

00 1

00

#### Decode: A= RF[IR[25:21]], B= RF[IR[20:16]], ALUOut = PC + Sign\_Ext(IR[15:0]) << 2);</p>

| PCWrite:<br>PCWriteCond:<br>IorD:            |               | Microin | structio | on:    |            |         |         |        |

|----------------------------------------------|---------------|---------|----------|--------|------------|---------|---------|--------|

| MemRead:<br>IRWrite:                         |               | ALUctrl | SRC1     | SRC2   | RegCtrl    | Memory  | PCWrite | Sequen |

| MemtoReg:                                    |               | Add     | PC       | ExtShf | Read       |         |         | Disp 1 |

| ALUSrcB:<br>ALUSrcA:<br>RegWrite:<br>RegDst: | )0<br>11<br>0 |         |          | w      | 'e'll tall | k about | soon.   | 1      |

# Sample Microinstruction (3) BEQ1: -> Ifetch,

IIM

# if (A=B) then PC= ALUout

Microinstruction:

|   | ALUctrl | SRC1 | SRC2 | RegCtrl | Memory | PCWrite     | Sequen |

|---|---------|------|------|---------|--------|-------------|--------|

| l | Sub     | Α    | В    |         | ,      | ALUout-cond | Fetch  |

5-11

## Put It All Together

| TIME |

|------|

|      |

|      |

|          | ALU       |      |         | Register  |           | PCWrite      |            |

|----------|-----------|------|---------|-----------|-----------|--------------|------------|

| Label    | control   | SRC1 | SRC2    | control   | Memory    | control      | Sequencing |

| Fetch    | Add       | РС   | 4       |           | Read PC   | ALU          | Seq        |

|          | Add       | РС   | Extshft | Read      |           |              | Dispatch 1 |

| Mem1     | Add       | Α    | Extend  |           |           |              | Dispatch 2 |

| LW2      |           |      |         |           | Read ALU  |              | Seq        |

|          |           |      |         | Write MDR |           |              | Fetch      |

| SW2      |           |      |         |           | Write ALU |              | Fetch      |

| Rformat1 | Func code | Α    | в       |           |           |              | Seq        |

| _        |           |      |         | Write ALU |           |              | Fetch      |

| BEQ1     | Sub       | Α    | в       |           |           | ALUOut-cond  | Fetch      |

| JUMP1    |           |      |         |           |           | Jump address | Fetch      |

What would a microassembler do?

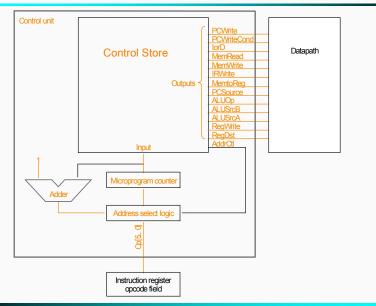

#### **Control Implementations**

- The big picture: **PCWriteCond** lorD VemRe Control Logic Vem\/\/rite RWhite VentoRed PCSouro Output ALUO<sub>D</sub> Ren/Mrit ReaDs Input 8888 8 8 ন্ত প্ত State register Instruction Register Opcode Field How to implement the control logic? - Random logic, memory-baed, mux-based, ...

- 5-14

IIN

#### **Memory-Based Implementation**

5-13

#### □ Important factors to consider when using a memory:

How many address lines?

#### So the ROM size is

- How many entries (or addresses) contain distinct values?

- many outputs are the same or don't cares so can be rather wasteful

### Alternatives for Control Implementation

#### □ Use hardwired random logic

- Efficient especially if you have a good CAD tool (not Xilins, ok)

- Not as flexible as memory-based

#### □ Can we do better?

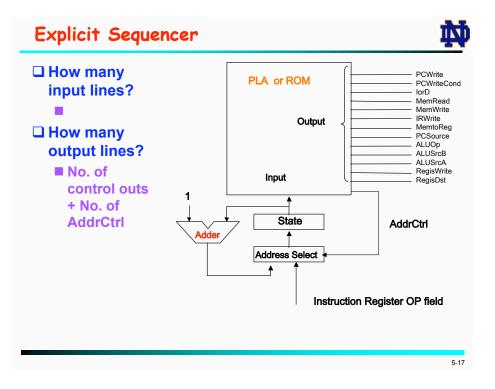

Use an explicit sequencer so avoid storing unused entries

How many output bits?

#### Address Select Logic

# Address Control Action 🙀

5-19

| State No. | Address-control action    | Value of AddrCtl |

|-----------|---------------------------|------------------|

| 0         | Use incremented state     | 3                |

| 1         | Use dispatch ROM 1        | 1                |

| 2         | Use dispatch ROM 2        | 2                |

| 3         | Use incremented state     | 3                |

| 4         | Replace state number by 0 | 0                |

| 5         | Replace state number by 0 | 0                |

| 6         | Use incremented state     | 3                |

| 7         | Replace state number by 0 | 0                |

| 8         | Replace state number by 0 | 0                |

| 9         | Replace state number by 0 | 0                |

# The Complete Design

5-18

IN

IN

#### Microcode: Trade-offs

- Distinction between specification and implementation is sometimes blurred

- □ Specification Advantages:

- Easy to design and write

- Design architecture and microcode in parallel

#### □ Implementation (off-chip ROM) Advantages

- Easy to change since values are in memory

- Can emulate other architectures

- Can make use of internal registers

- □ Implementation disadvantages, SLOWER now that:

- Control is implemented on same chip as processor

- ROM is no longer faster than RAM

- No need to go back and make changes

#### Exceptions

IIM

5-21

IN

- □ Exceptions: unexpected events from within the processor

- arithmetic overflow

- undefined instruction

- switching from user program to OS

- Interrupts: unexpected events from <u>outside</u> of the processor

I/O request

- **Consequence: alter the normal flow of instruction execution**

#### □ Key issues:

- detection

- action

- > save the address of the offending instruction in the EPC

- > transfer control to OS at some specified address

- Exception type indication:

- status register

- interrupt vector

5-22

### **Exception Handling**

- **Types of exceptions considered:**

- undefined instruction

- arithmetic overflow

- □ MIPS implementation:

- EPC: 32-bit register, EPCWrite

- Cause register: 32-bit register, CauseWrite

- > undefined instruction: Cause register = 0

- > arithmetic overflow: Cause register = 1

- IntCause: 1 bit control

- Exception Address: C0000000 (hex)

#### **Detection:**

- undefined instruction: op value with no next state

- arithmetic overflow: overflow from ALU

#### **Action:**

- set EPC and Cause register

- set PC to Exception Address

# Datapath with Exception Handling

# 政